| ❤️ | 💛 | 💙 | 💚 |

|---|---|---|---|

| 高优先级 | 中优先级 | 低优先级 | / |

| 未完成 | 未完成 | 未完成 | 已完成 |

2025/7/17

- 💚 10 tag release邮件

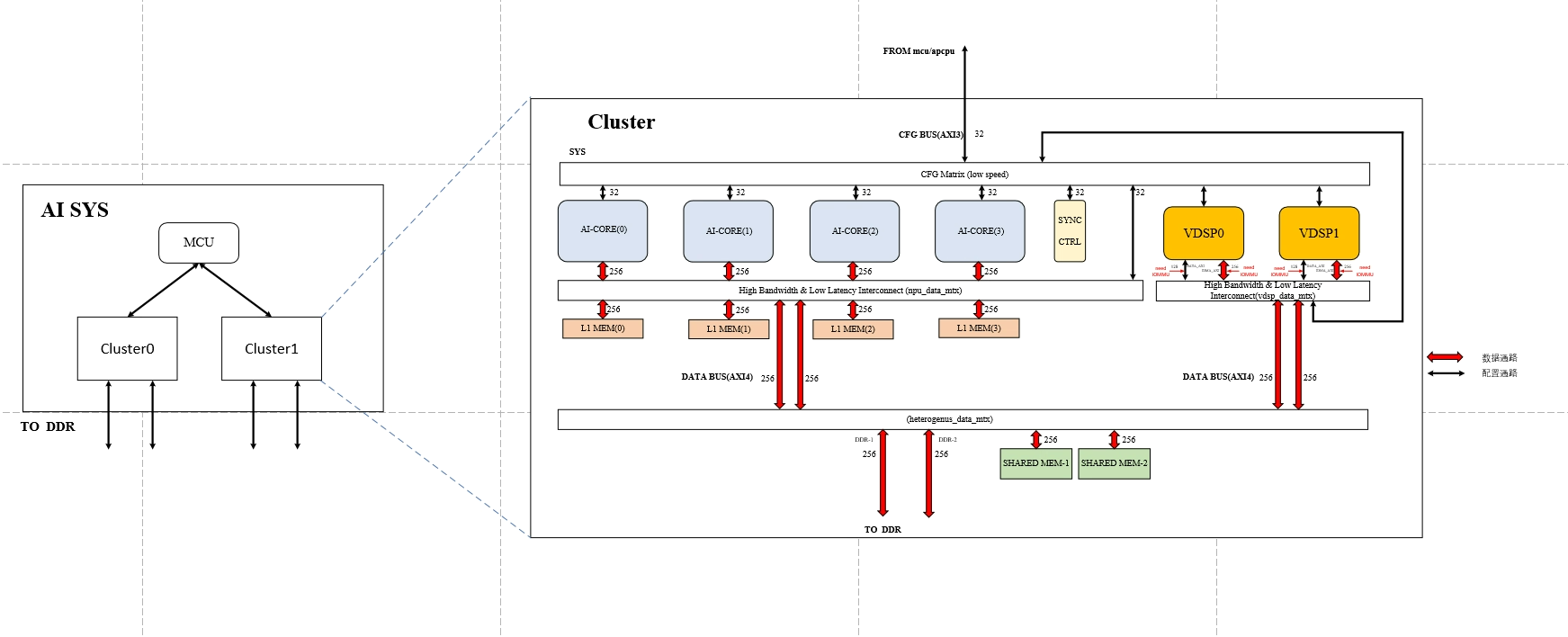

- 💚 s6p ai arch更新

2025/7/18

- 💚 changelist

2025/7/29

- 💚 后仿波形确认

- 💚 uniclk&clk_core内部没有rst同步模块,需要规范软件对ai sys软复位行为

- 💚 mem floating——ongoing

- 💚 ai_share_mem addr[15] deaddead

- 💚 确认stc R24-01-02最新check list是否还存在问题

- 💚 ai clk_glue 修改完毕

- 💚 地址回绕问题确认

- 💚 worklog填写d

- 💚 sync_buf_idma中regfile2p_16x289

- 💚 ocm 1MB计算过程 ddl 8.4

- 🔵 sync_buf wr/rd问题

- 🔵 画lowpower/reset arch/clock arch 参考mm sys

- 🔵 clk gui & dvfs 了解&try run

- 💚 加入26m的源以后,为何能保证复位的时候没有时钟

- 硬复位:26m clk有sys专用gate,pmu给ai上电复位时,pmu会在ai复位之前gate该时钟,复位释放之后才会释放,ai的配置时钟sel默认在26m,以此保证硬复位过程中不会有时钟

- 软复位:无法确保,没有对应gate反压,但S6软件不会使用

- 💚 77对比21 为何svt增加,lvt减少?

- 💚 lp stat?mem_fw_eb 改成其他值配一下?

2025/7/31

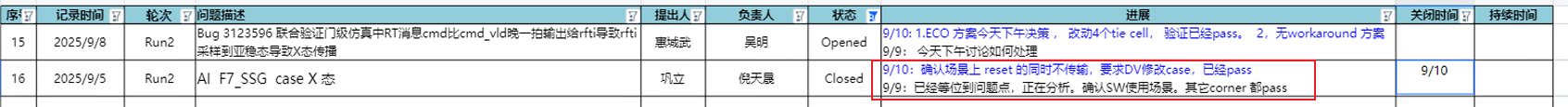

- 💚 bugzila

- 💚 changelist review aciton追踪

- 💚 changlist加上还没修改代码的点

- 💚 让npu ip出一版带ulvt u2p memory的版本

2025/8/1

- 💚 flat cdc 清理

- 💚 changelist review及action追踪

- 💚 matrix的write outstanding是否能够达到要求

2025/8/5

- 💚 ai low power arch更新

- 💚 ai clock arch绘制

2025/8/8

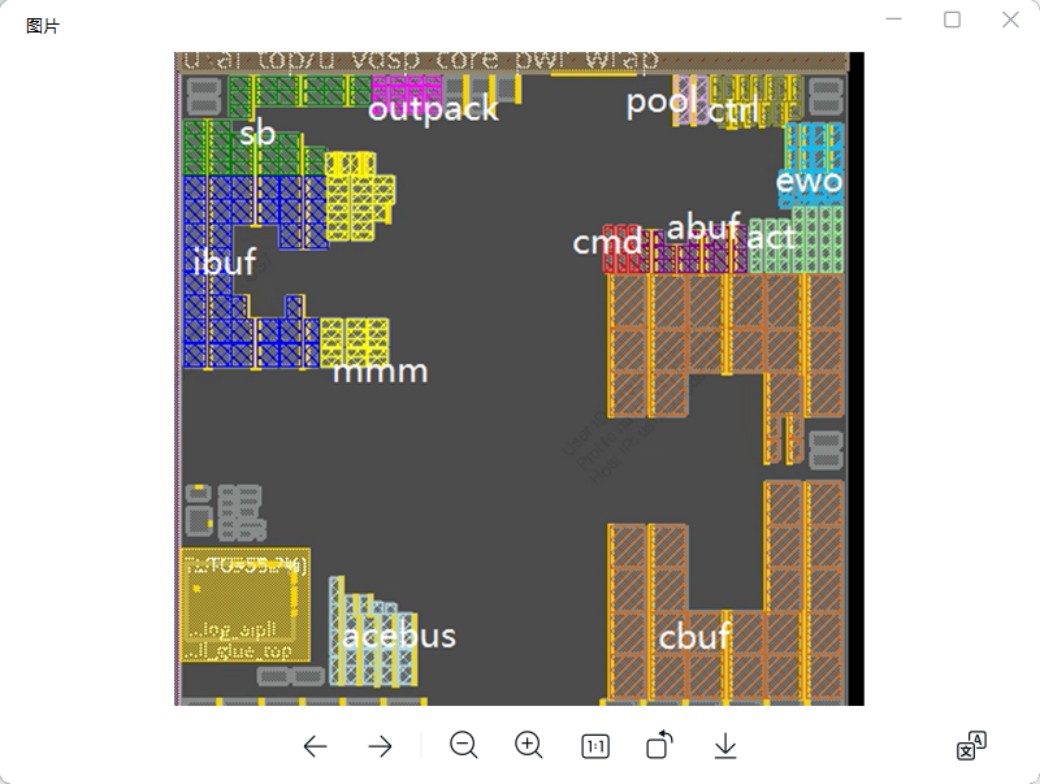

- 💚 沟通vdsp插slice问题

- vau相关的aw/ar通路是否能优化,不插slice

- 将vau位置上挪后(加region),vdsp2vau得到改善,但是vau2mtx 违例增加到0.13

- mtx2mtx r通道路径,违例达0.33

- cfg_s2 -> vdsp suboridinate也存在timing问题,约0.17

- 需要将reg_slice配置为打拍

- 💚 dbg bus是否为sys最新版本

- 💚 pcie,抓level shifter 延时

- 💚 ase 跑完数据对比错误

2025/8/11

- 💚 S6P NPU+VDSP加PowerSwitch 实验结果讨论

- 预计SYS内增加power switch后,IR可能会恶化1.5%到2.5%,可能需要在额外抬压50mV到0.90V才能改善IR问题

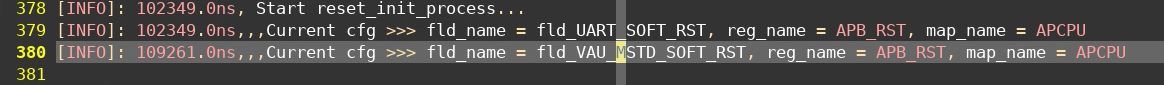

- 💚 s6 ai后仿rst需要确认timing violation,预计只有clk core内部存在x态

2025/8/20

- 💙 vc里qogirs6pro_define.v ?

- 💚 和泽峰确认mem_fw连接

- 💚 和bingwei确认ai_clk_glue.V

2025/9/1

- 💚 AI系统说明书,有两个AISYS的问题修改

- 💚 ai sys cv对齐会议

- 💚 截止9.3 PBS ai sys修改

- 删除tower

- 删除axi top2ai异步桥?

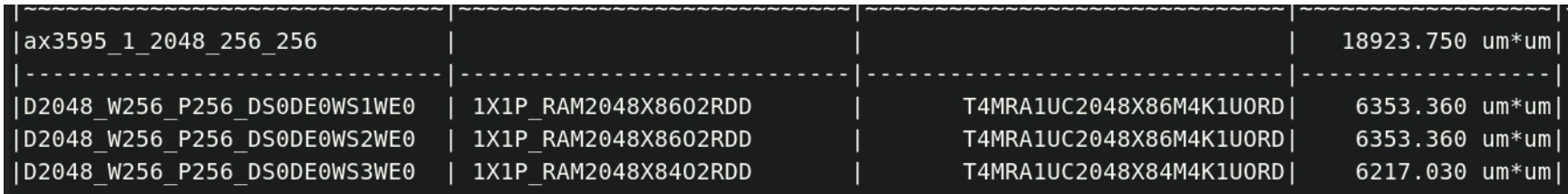

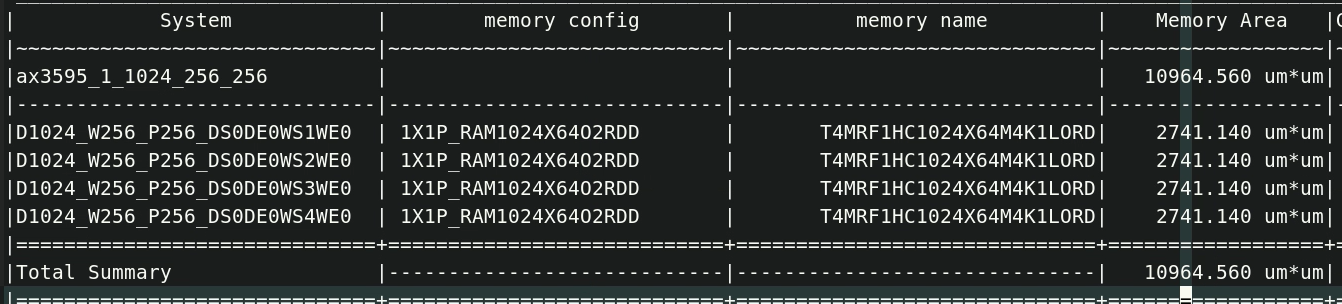

- 💙 NPU 64K sram优化

- before:2个64KB的SRAM

- 2048深度,256bit

- after:2个32KB的SRAM

- 1024深度,256bit

- conclusion:预计减小0.0159mm2(综合面积)

- before:2个64KB的SRAM

2025/9/2

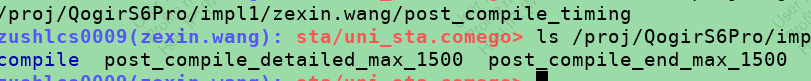

- 💛 sta检查时钟周期正确

- 💛 ai2pcie 通路

- matrix+异步桥w端

- matrix具体细节待确认

- 💚 pcie port fix

- async bridge w

- lp_stat_ai2pcie

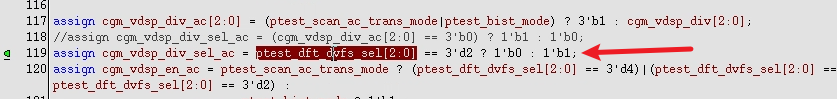

- 💚 ai clk glue还是有点问题,div_sel应该怎么选

- 改之前

- 改之后

2025/9/4

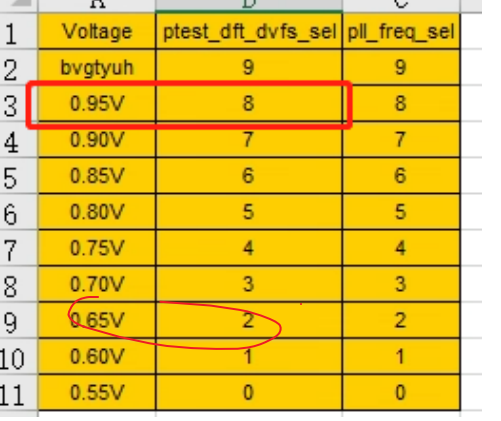

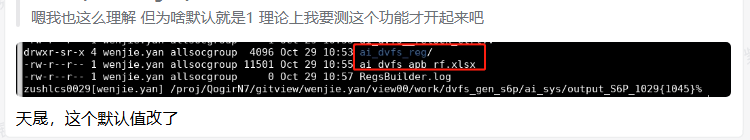

- 💛 dvfs 更新ipa后对比rtl

- 💛 pr 更新timing 查看

- 💛 slv fw进版更新

- 💛 dbg bus修改

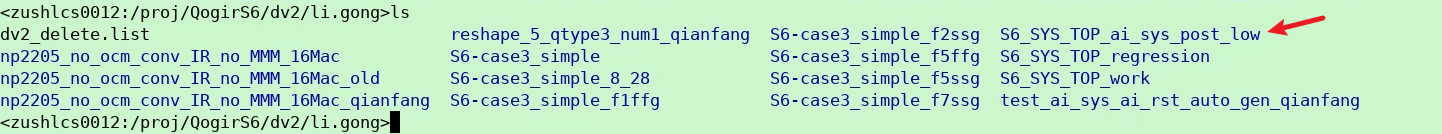

- 💛 dv后仿 vio查看

2025/9/5

- 💚 tower 006进版修改port位宽

2025/9/8

- 💛 ocm slack

- 现在大是因为multi bit,导致绕线很多

- 💛 data path是否合理

2025/9/9

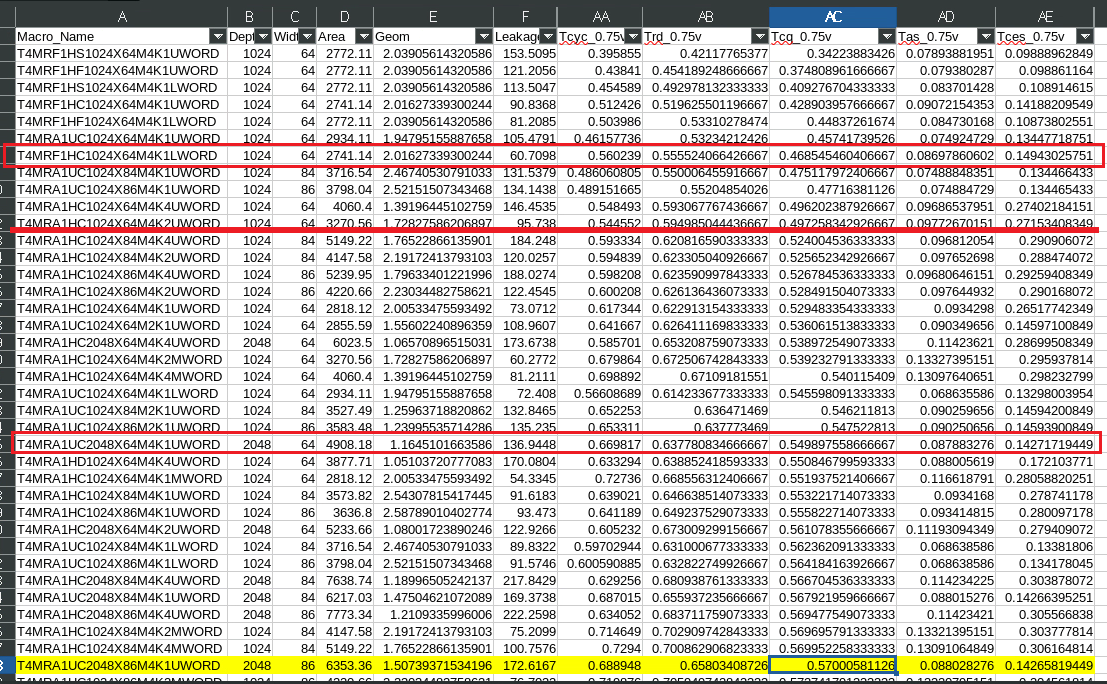

- 💛 clk tree是ulvt ll,瑞奇推荐使用ulvt

- 💛 后仿波形确认——第二轮回归的结果,vio还是得看,多关注下第一轮重点看的vio

- 💙 ai实验室有个偏技术项目的开发, 主要是一个可配置(预计96T)算力ai sys层的开发

- 💛

2025/9/11

- 💛 ai2pcie修改点总结

- 加main_mtx_s4的lpc,asb_ai2pcie也用这个

- asb_ai2pcie rst 用main_mtx的

- mtx axi4, asb axi3

- mtx lock 1bit, asb lock 2bit

- 需要多开3个ep的mailbox

- ❤️ dvfs ipa待合入,需要开3bit port

- ❤️ 更新后的slv fw也需合入

2025/9/16

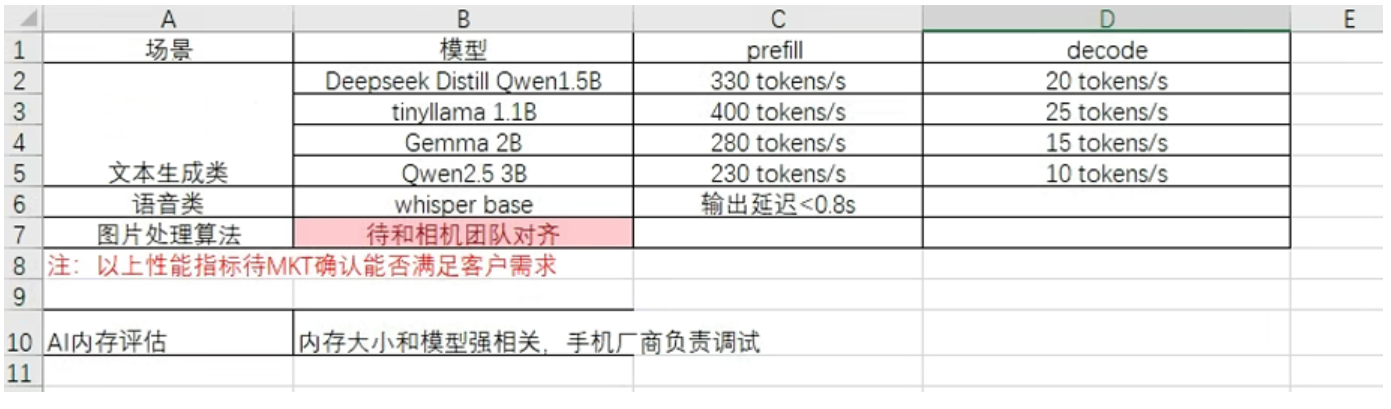

- 💛 s6p ai性能指标

- 后仿复位改安全复位case

- vau软复位改成安全复位之后,会force vdsp传输,等到总线idle之后再发起复位,case pass

2025/10/13

- 💙 sdc加入0.85v

- 💙 mtx & slv fw给vdsp decode

2025/10/24

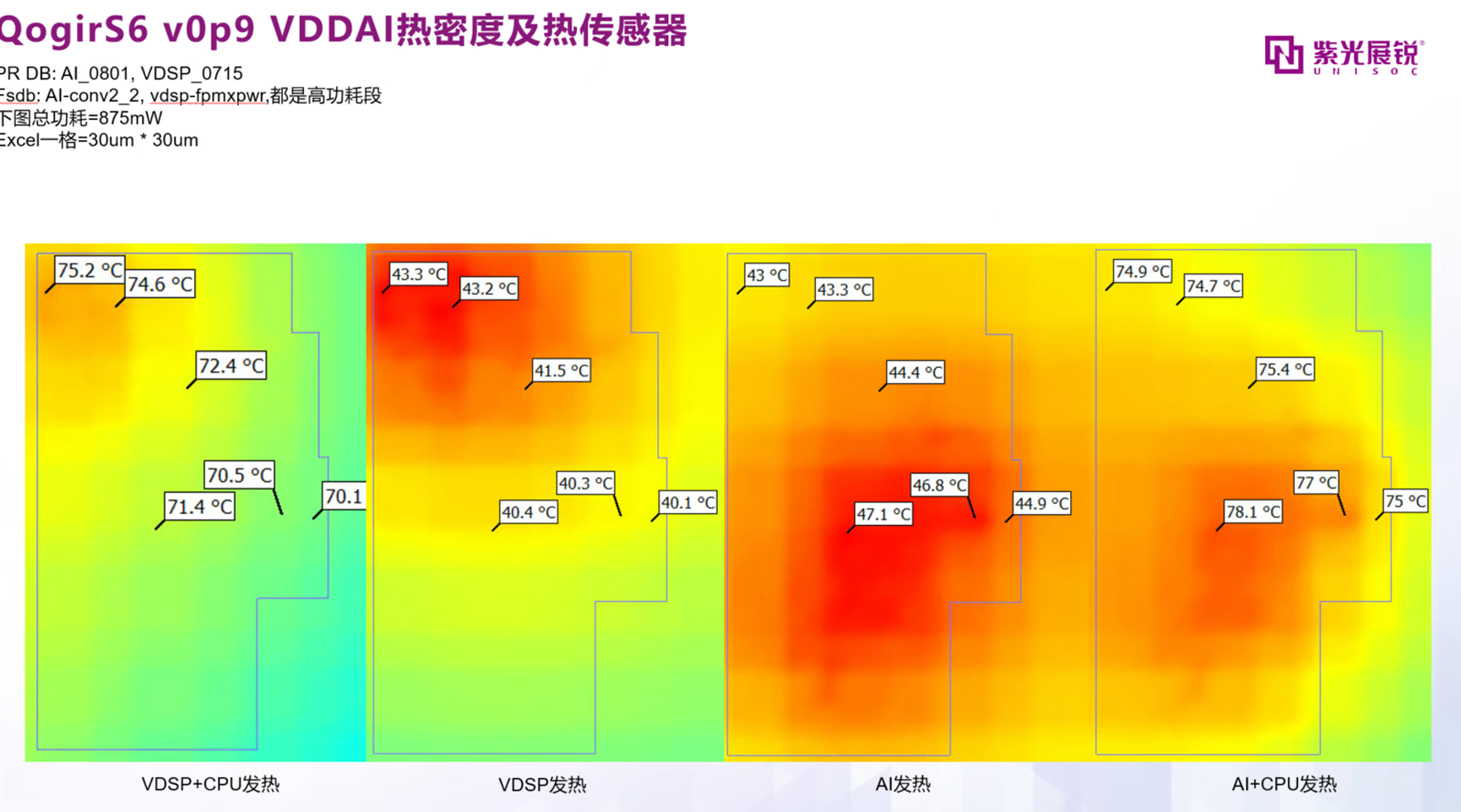

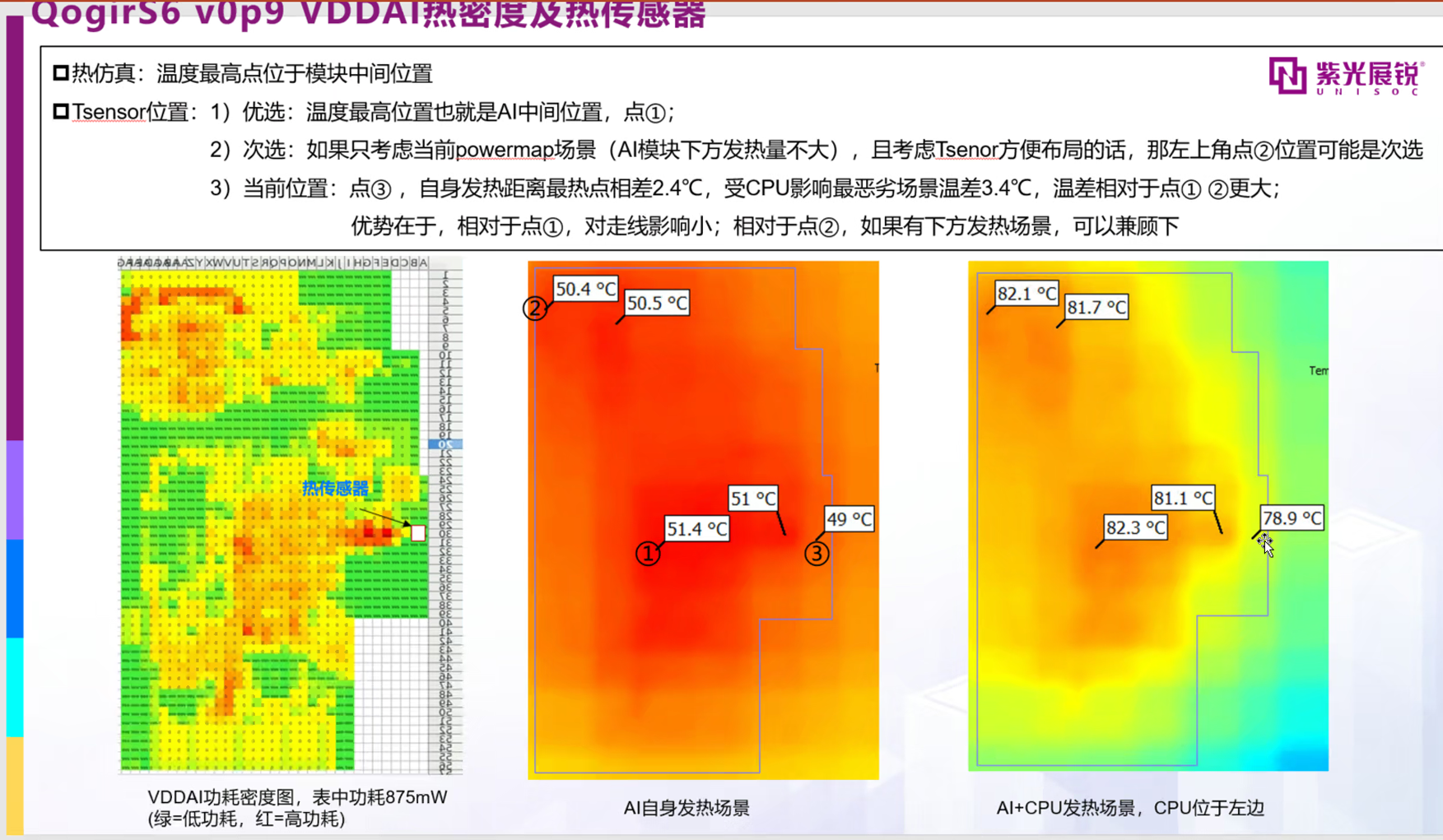

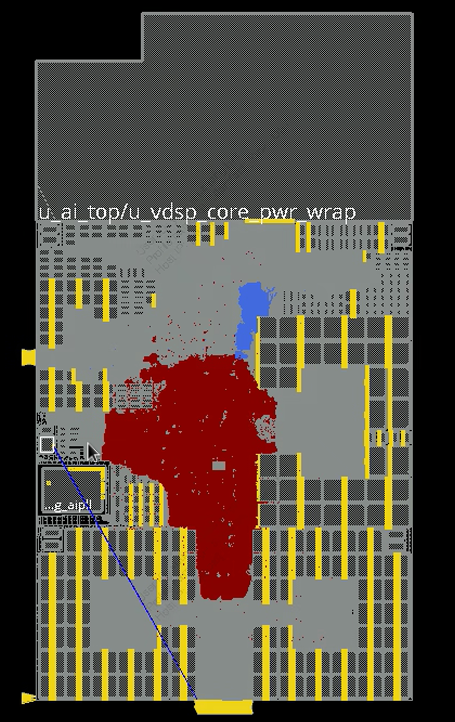

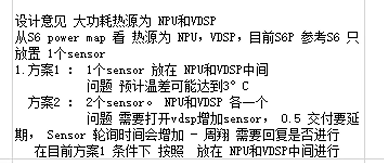

- 💙 s6建议三档(0以下/常温/高温)

- 需不需要增加一个thm——待讨论

- s6p后续仿真,定thm具体位置

2025/10/28

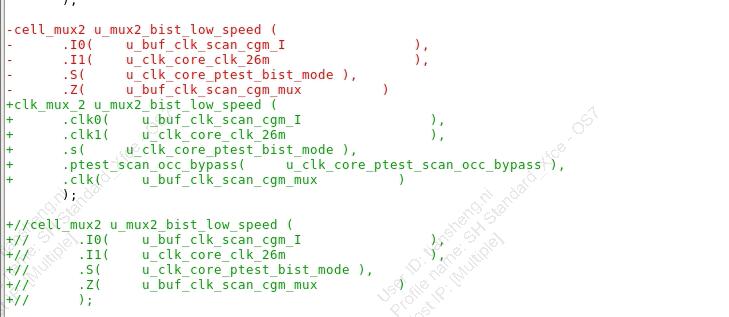

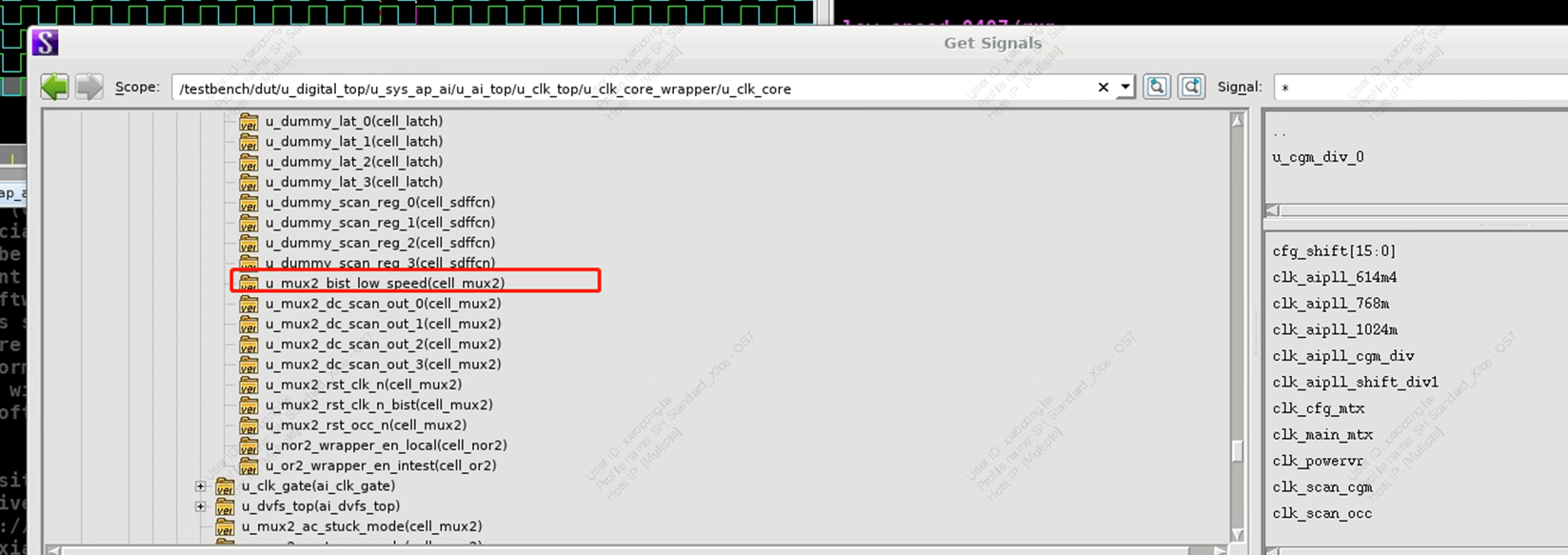

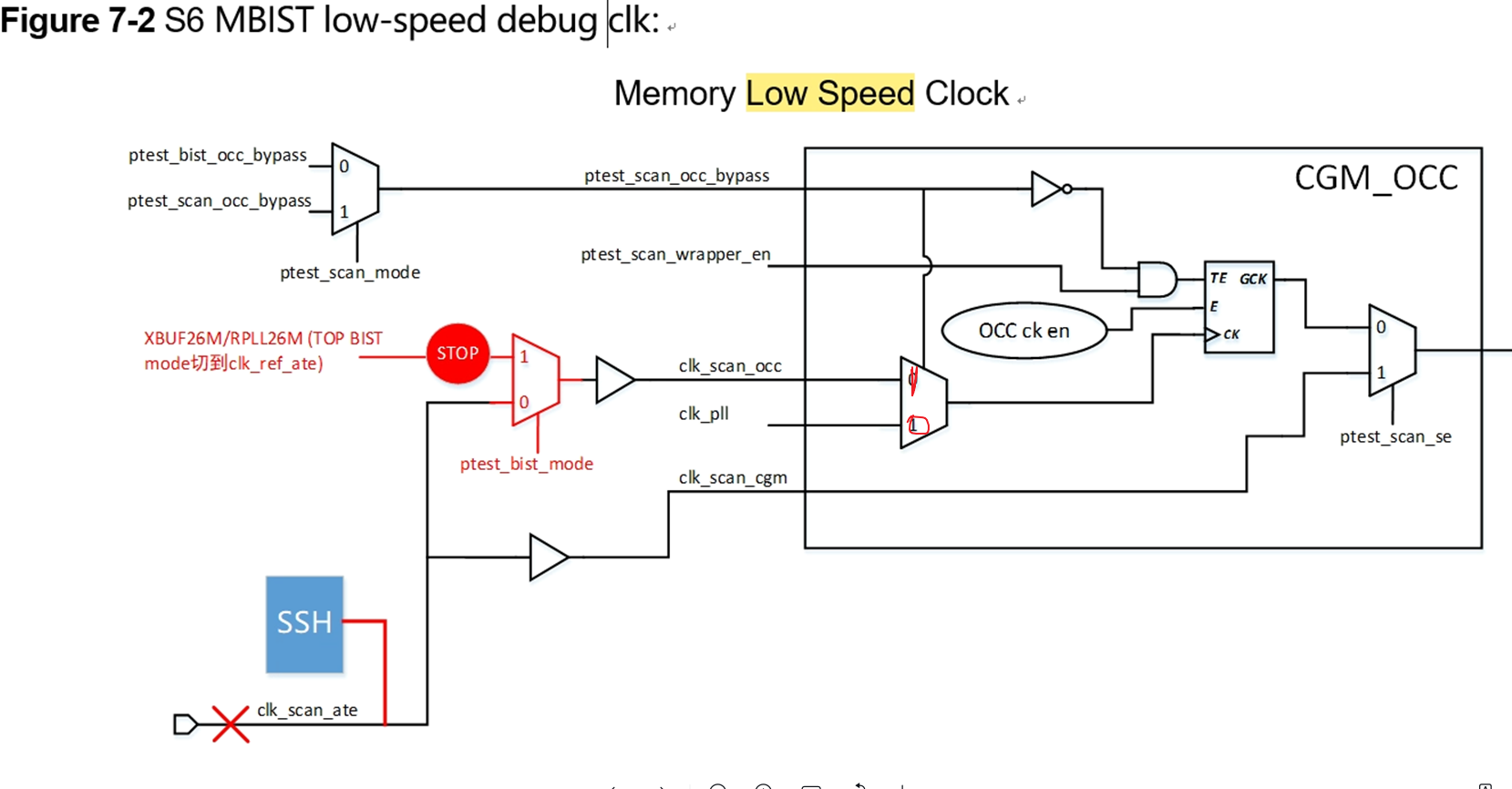

- erc报出来有clk on data

- 换了clk_mux

- 但得换ckmux,否则在occ_bypass为1时会切到clk_scan_ate,后者为内部时钟,非外部低速时钟,影响npu/vdsp在低速下的binning

-

cbuf memory有

-

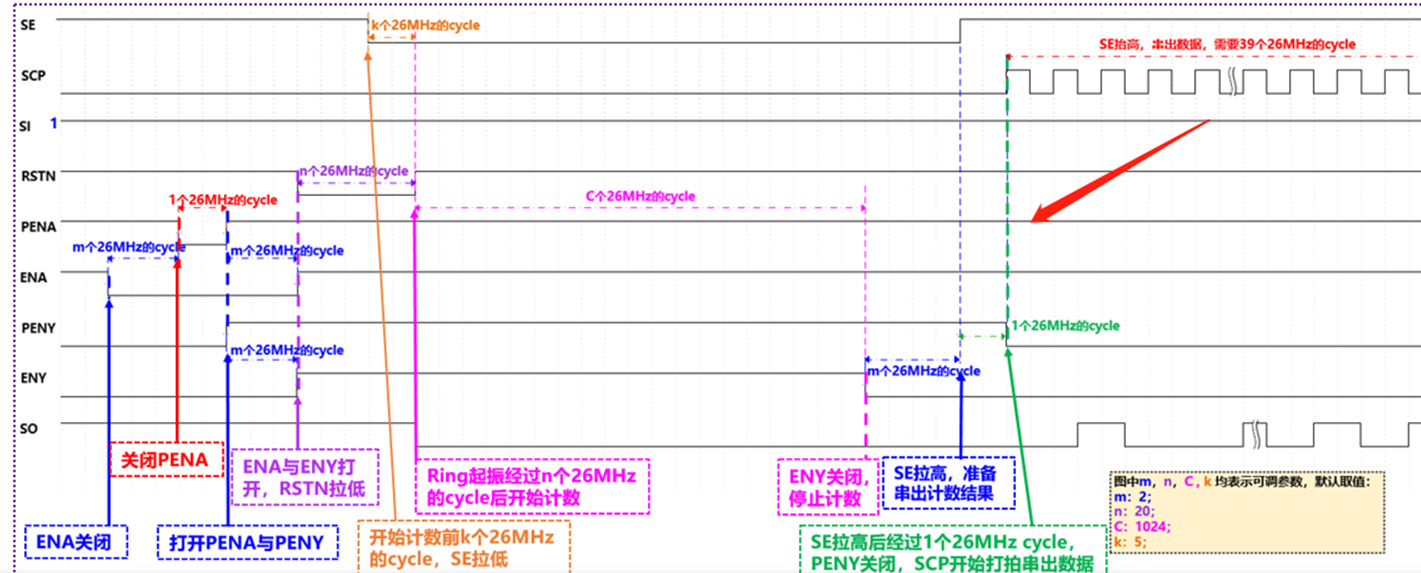

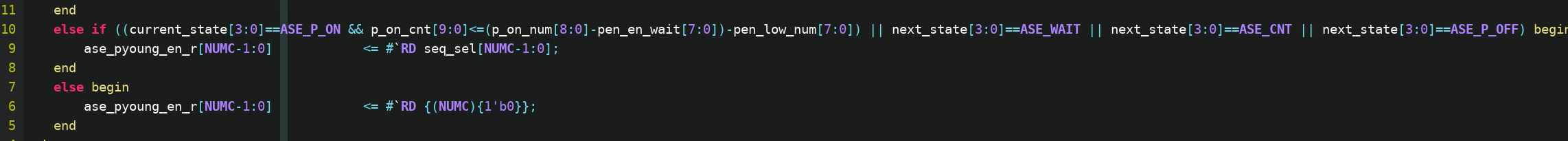

💙 ase controller PENY晚于SE一派拉低

- 💛 hld上传

- ❤️ fifo wr cmd和data是否能分离

- dvfs busy拉到clk cfg mtx

- 反标featurelist

- checklist

- changelist

- 💛 面积变更项准备材料

- ❤️ uniclk mode默认值改成0

- async_bridge_w_ai2pcie*-/ 时钟接错

- dvfs ipa的en修改默认值

2025/11/14

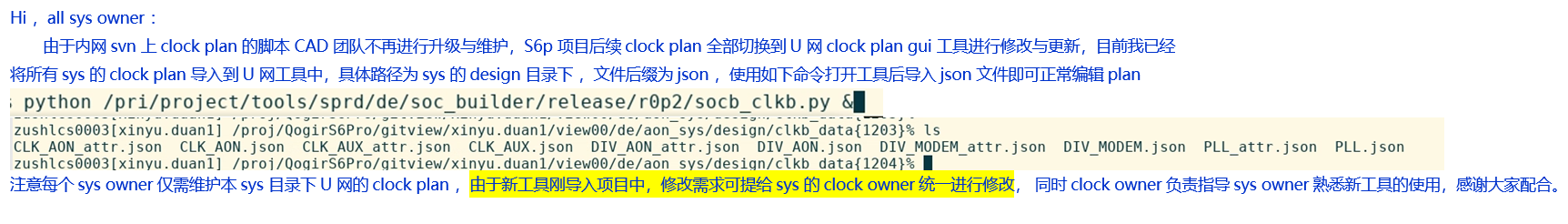

- clk plan

- 需要pull一下top